A IBM apresentou na semana passada que construiu a capacidade de fornecer chips de transistores de 2 nm. A situação atual com arte é geralmente em torno de 5 nm ou 7 nm, então esse é um salto incrível, apesar do fato de que avaliar tamanhos entre vários fabricantes não é sempre certo.

Mais chamativo do que seu tamanho é que esses chips provavelmente serão desenvolvidos com um suposto plano de “nanosheet”. A maioria dos transistores chiques são fundamentalmente baseados em “FinFET”, o ponto em que os fluxos de corrente através do semicondutor são estendidos diretamente em um equilíbrio. Nanosheet ou transistores “gate-all-around” invertem esse equilíbrio diretamente em uma pilha de tiras individuais específicas, e o plano deve ser capaz de atualizar a eficácia da energia e permitir que os projetos alterem essencialmente as propriedades {elétricas} de várias partes do chip . O FinFET é típico desde 2011, portanto, mostrar um novo modelo de semicondutor de plástico é um arranjo sensatamente enorme no mundo dos semicondutores.

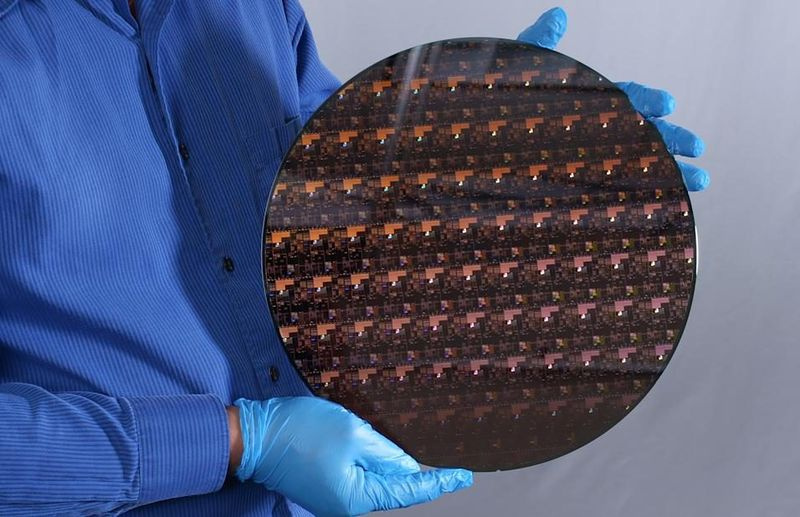

Em um salto significativo para a frente, a IBM relatou o primeiro chip de 2nm de seu tipo dependente da inovação de nanofolhas. A organização disse que este chip ajudaria a avançar no negócio de semicondutores e levaria em conta seu interesse em desenvolvimento de chips. Os processadores de 2nm podem quadruplicar a vida útil da bateria dos PDAs. À luz do uso normal, a bateria do telefone pode durar até quatro dias. O chip oferece 45% melhor e usa 75% menos energia do que os atuais chips de nó de 7nm mais excepcionais.

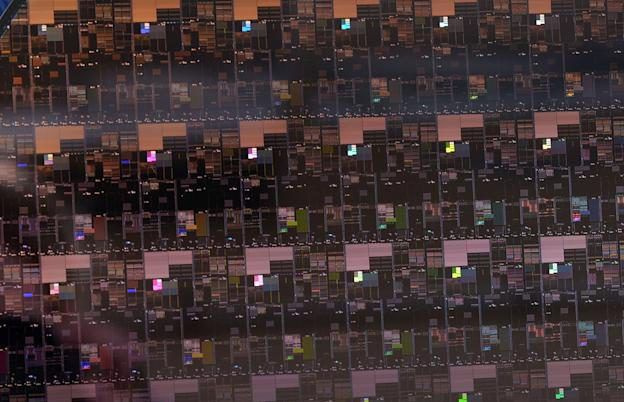

A combinação de força/execução acelera a virada dos eventos e a transmissão dos estágios de computação de vanguarda, de ponta e outros estágios de computação transmitidos por meio de condições de nuvem cruzada e pedais de aceleração de criptografia trabalhados para funcionar com PCs quânticos. A nanotecnologia de 2 nm pode obrigar até 50 bilhões de transistores em um chip do tamanho de uma unha. Mais transistores em um chip capacitarão os originadores a desenvolver responsabilidades de ponta, como IA, computação em nuvem, segurança imposta por hardware e criptografia.

A nova contribuição da IBM ainda está no estágio de verificação da ideia e pode levar algum tempo até que seja acessível comercialmente. No momento, as organizações adversárias da IBM, Samsung e TSMC, estão entregando chips de 5 nm em suas fundições. A TSMC havia declarado antes que começará a fornecer chips de 4 nm antes do final de 2021 e executará chips de 3 nm continuamente 50% de 2022. Os chips de 7 nm da Intel ainda estão em andamento.

Como a IBM surgiu com isso?

O termo nanosheet foi criado pela primeira vez nos laboratórios da IBM em 2012, quando seu grupo de especialistas tratou de outra engenharia de gadgets. O objetivo era construir uma opção apropriada para a estrutura de nanofios mainstream. O segundo Eureka da IBM acompanhou a engenharia de nanofolhas, que oferecia as vantagens eletrostáticas do nanofio juntamente com a espessura necessária para uma melhor execução.

Com essa mistura de destaques, as nanofolhas conquistaram o FinFET, estrutura semicondutora predominante naquele momento. De qualquer forma, o negócio estava rapidamente ultrapassando o plano FinFET. Os planejadores tentaram empacotar mais transistores, mas isso provocou derramamento de semicondutores.

A inovação FinFET recebe o nome da construção FET e se assemelha a um monte de lâminas. Nesta construção, os elétrons percorrem delicadas lâminas verticais, em vez de uma superfície plana, para passar pelos transistores. Então, novamente, as nanofolhas empilham transistores uns sobre os outros para moldar designs em camadas. O principal semicondutor de 2 nm é o novo gadget de tensão multilimiar (Multi-Vt) com níveis de derramamento que cruzam tamanhos de três ordens. Ele permite que os fabricantes escolham um grau superior de execução.